并行设置,采样时钟反相操作。子ADC系统传递函数之间不可避免的微小失配会导致杂散谐波(tones),能够显著降低可实现的动态范围。在这种ADC中有四种类型的误差:

在实际应用中,DC偏置误差很简单,可通过数字校准来处理。带宽误差最难应对,通常是通过精心的设计和布局来使误差减小。在本文中,我们将重点讨论增益和时序误差校准,因为他们是造成动态范围损失的主要原因。

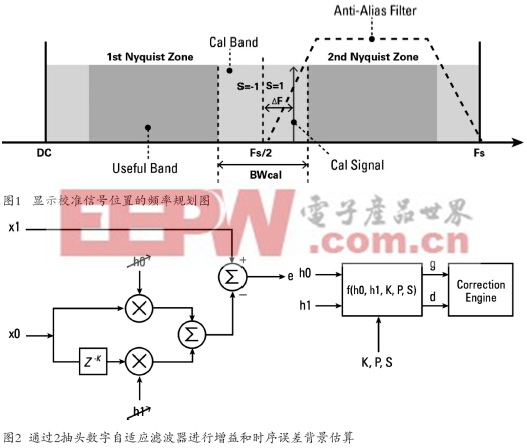

一般情况下,ADC的奈奎斯特带宽(Nyquist bandwidth)从未被充分使用,其中的一小部分通常专门为抗混叠(anti-aliasing)滤波器的滚降特性预留。这个未被使用的频段可用来引入约束校准信号。可选择正弦波用于校准,因为它很容易生成高纯度频谱,并可施加两个主要限制:

1. 幅度保持足够小,以避免对动态范围产生任何影响,同时提供足够的估算精度。实验表明,对于一个14位的ADC,-40dBFS到-35dBFS的幅度范围为最佳。

![]()

其中,Fs是TIADC采样频率,P和K为待指定的整数,S=1,取决于校准信号相对于奈奎斯特区边缘的位置(见图1)。校准信号可以很容易地在片上通过使用小数N分频锁相环(PLL)以ADC时钟作为参考信号来产生。选择足够高的K值,校准信号的谐波会在有用频带之外混叠,可降低对于滤波的要求。通过使用在PLL输出端的可编程衰减器能够实现摆幅的调整。

如果校准信号作为输入,x0和x1分别代表两个子ADC的输出,这可用等式1表示,而下面的等式2则将这两路信号联系起来(此处已忽略噪声):